- 您现在的位置:买卖IC网 > Sheet目录3890 > PIC18C858T-I/PT (Microchip Technology)IC MCU OTP 16KX16 CAN 80TQFP

PIC18CXX8

DS30475A-page 138

Advanced Information

2000 Microchip Technology Inc.

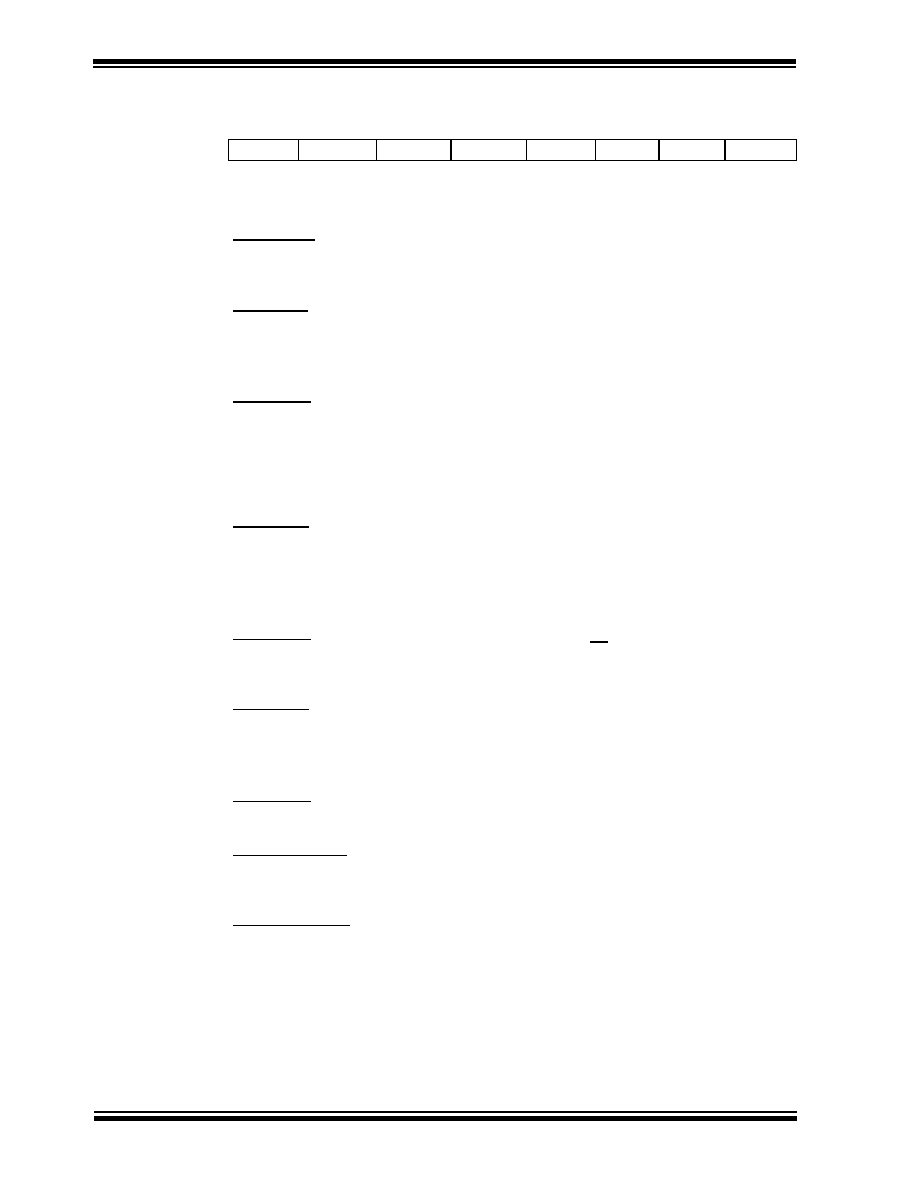

REGISTER 15-2:

SSPCON1 REGISTER

R/W-0

WCOL

SSPOV

SSPEN

CKP

SSPM3

SSPM2

SSPM1

SSPM0

bit 7

bit 0

bit 7

WCOL: Write Collision Detect bit

Master mode:

1

= A write to the SSPBUF register was attempted while the I2C conditions were not valid for a

transmission to be started

0

= No collision

Slave mode:

1

= The SSPBUF register is written while it is still transmitting the previous word (must be

cleared in software)

0

= No collision

bit 6

SSPOV: Receive Overflow Indicator bit

In SPI mode:

1

= A new byte is received while the SSPBUF register is still holding the previous data. In case

of overflow, the data in SSPSR is lost. Overflow can only occur in Slave mode. In Slave

mode, the user must read the SSPBUF, even if only transmitting data, to avoid setting

overflow. In Master mode, the overflow bit is not set since each new reception (and

transmission) is initiated by writing to the SSPBUF register. (Must be cleared in software.)

0

= No overflow

In I2C mode:

1

= A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a

"don’t care" in Transmit mode. (Must be cleared in software.)

0

= No overflow

bit 5

SSPEN: Synchronous Serial Port Enable bit

In both modes, when enabled, these pins must be properly configured as input or output.

In SPI mode:

1

= Enables serial port and configures SCK, SDO, SDI, and SS as the source of the serial port

pins

0

= Disables serial port and configures these pins as I/O port pins

In I2C mode:

1

= Enables the serial port and configures the SDA and SCL pins as the source of the serial

port pins

0

= Disables serial port and configures these pins as I/O port pins

bit 4

CKP: Clock Polarity Select bit

In SPI mode:

1

= Idle state for clock is a high level

0

= Idle state for clock is a low level

In I2C Slave mode:

SCK release control

1

= Enable clock

0

= Holds clock low (clock stretch). (Used to ensure data setup time.)

In I2C Master mode

Unused in this mode

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18C658T-I/PT

IC MCU OTP 16KX16 CAN 64TQFP

PIC16LC717T-E/SS

IC MCU OTP 2KX14 A/D PWM 20SSOP

PIC16LC771T/SO

IC MCU OTP 4KX14 A/D PWM 20SOIC

PIC16LC771T-E/SO

IC MCU OTP 4KX14 A/D PWM 20SOIC

PIC16C771T-E/SO

IC MCU OTP 4KX14 A/D PWM 20SOIC

PIC16LC770T/SS

IC MCU OTP 2KX14 A/D PWM 20SSOP

PIC16LC717T-I/SO

IC MCU OTP 2KX14 A/D PWM 18SOIC

PIC16LC771T/SS

IC MCU OTP 4KX14 A/D PWM 20SSOP

相关代理商/技术参数

PIC18F1220-E/ML

功能描述:8位微控制器 -MCU 4KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-E/P

功能描述:8位微控制器 -MCU 4KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-E/SO

功能描述:8位微控制器 -MCU 4KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-E/SS

功能描述:8位微控制器 -MCU 4KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-H/ML

功能描述:8位微控制器 -MCU 4KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-H/P

功能描述:8位微控制器 -MCU 4KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-H/SO

功能描述:8位微控制器 -MCU 4KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-H/SS

功能描述:8位微控制器 -MCU 4KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT